Testen sicherheitsrelevanter Hardware: Ingenieure zeigen, nicht alle Fehler beeinflussen Software

Christian Bartsch war als Erstautor maßgeblich an der Studie beteiligt. Foto: Koziel/TUK

Sie sorgen etwa dafür, dass ein Zug rechtzeitig bremst, dass die Landeklappen beim Flugzeug ausfahren oder dass eine Maschine unmittelbar stoppt, wenn die Hand eines Arbeiters zu nah an die Säge kommt – Embedded Systems.

Diese kleinen Rechner gewährleisten die Sicherheit solcher Techniken. Um Fehler früh aufzuspüren, muss die Hardware regelmäßig getestet werden. Hinzu kommt:

„In solchen Prozessoren werden die Hardware-Komponenten immer kleiner. Das macht sie anfälliger für Fehler“, sagt Christian Bartsch, Doktorand im Lehrgebiet „Entwurf Informationstechnischer Systeme“ bei Professor Dr. Wolfgang Kunz an der Technischen Universität Kaiserslautern (TUK). Faktoren wie Alterung oder hohe Temperaturen führen dazu, dass Bauteile bei solchen Chips schneller verschleißen.

Auf dem Markt gibt es eine Vielzahl solcher Testverfahren. Diese laufen automatisch ab, ohne dass der Nutzer etwas davon mitbekommen. Die gesamte Hardware (HW) zu überprüfen, kostet Zeit und Energie, die die Leistungsfähigkeit des Systems negativ beeinflusst.

Das Kaiserslauterer Forscherteam hat nun ein Modell entwickelt, mit dem sie die Auswirkungen von Hardwarefehlern auf das Verhalten der Software analysieren. „Wir haben darin an verschiedenen Stellen der Hardware Fehler eingebaut“, fährt der Doktorand fort.

Dieses Modell vergleichen die Ingenieure mit einer fehlerfreien Variante, bei der die Hardware reibungsfrei läuft. Bei ihren Tests haben die Ingenieure jeweils einzelne Fehler, aber auch Mehrfachfehler untersucht.

„Wir haben geprüft, ob sie Auswirkungen auf die Software haben“, sagt Bartsch, der auch Erstautor der Studie ist. Dabei haben die Wissenschaftler herausgefunden, dass ein Großteil der Fehler keine Auswirkung auf die Software hat. „Dieser Anteil liegt bei 33 Prozent“, so Bartsch.

Für das Testen von sicherheitsrelevanten Systemen bedeutet dies: „Es reicht sich auf bestimmte Stellen zu konzentrieren, bei denen Fehler auch für die Software von Bedeutung sind“, so der Forscher. Da solche Prüfverfahren zeitaufwendig sind und Energie verbrauchen, könnten sich auf diese Weise auch Kosten einsparen lassen. Außerdem werden Fehler schneller gefunden, wenn solche Tests nur bestimmte Bereiche in den Fokus nehmen.

„Unsere Ergebnisse zeigen, dass Testverfahren künftig effizienter gestaltet werden können“, fährt Bartsch fort. Die Methode der Kaiserslauterer Forscher ermöglicht es zum Beispiel auch, Schutzmechanismen für Hardware-Fehler zu zertifizieren.

Bei sicherheitsrelevanten elektrischen Systemen in PKWs gibt es dafür beispielsweise derzeit einen bekannten Standard (ISO-Norm 26262). „Für bestimmte Hardwarefehler ließen sich etwa Schutzmechanismen entwickeln, mit denen Unternehmen analysieren können, ob diese auch ausreichen.“

Die Arbeit haben die Kaiserslauterer Ingenieure im vergangenen Jahr in der renommierten Fachzeitschrift „Journal of Electronic Testing – Theory and Applications“ (JETTA) publiziert.

Auf der führenden Tagung für Tests und Fehlertoleranzen, der International Test Conference (ITC), im US-amerikanischen Phoenix (Arizona) wurden sie dafür kürzlich mit dem Preis für die beste Publikation in JETTA ausgezeichnet. Verliehen wird diese Auszeichnung vom Test Technology Technical Council (tttc) des Institute of Electrical and Electronics Engineers (IEEE), dem weltweiten Berufsverband der Ingenieure.

Christian Bartsch

Entwurf Informationstechnischer Systeme

E-Mail: bartsch(at)eit.uni-kl.de

Tel.: 0631 205-2608

Die Studie: „A HW/SW Cross-Layer Approach for Determining Application-Redundant Hardware Faults in Embedded Systems”

DOI: 10.1007/s10836-017-5643-3

Media Contact

Alle Nachrichten aus der Kategorie: Informationstechnologie

Neuerungen und Entwicklungen auf den Gebieten der Informations- und Datenverarbeitung sowie der dafür benötigten Hardware finden Sie hier zusammengefasst.

Unter anderem erhalten Sie Informationen aus den Teilbereichen: IT-Dienstleistungen, IT-Architektur, IT-Management und Telekommunikation.

Neueste Beiträge

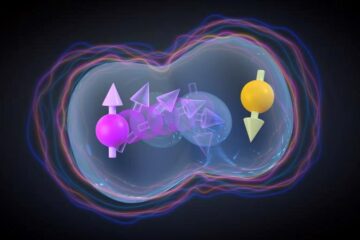

Experiment öffnet Tür für Millionen von Qubits auf einem Chip

Forschenden der Universität Basel und des NCCR SPIN ist es erstmals gelungen, eine kontrollierbare Wechselwirkung zwischen zwei Lochspin-Qubits in einem herkömmlichen Silizium-Transistor zu realisieren. Diese Entwicklung eröffnet die Möglichkeit, Millionen…

Stofftrennung trifft auf Energiewende

Trennkolonnen dienen der Separation von unterschiedlichsten Stoffgemischen in der chemischen Industrie. Die steigende Nutzung erneuerbarer Energiequellen bringt nun jedoch neue Anforderungen für einen flexibleren Betrieb mit sich. Im Projekt ColTray…

Kreuzfahrtschiff als Datensammler

Helmholtz-Innovationsplattform und HX Hurtigruten Expeditions erproben neue Wege in der Ozeanbeobachtung. Wissenschaftliche Forschung nicht nur von speziellen Forschungsschiffen aus zu betreiben, sondern auch von nicht-wissenschaftlichen Schiffen und marinen Infrastrukturen –…